Aplicación de la personalización de IP para mejorar los chips de IA: un estudio de caso

[ad_1]

Hoy en día, cada fundición de semiconductores ofrece una amplia gama de bibliotecas para sus procesos. También hay una amplia gama de bloques de propiedad intelectual (IP) de terceros disponibles. ¿Quién necesita personalización cuando la propiedad intelectual de fundición y de terceros sigue creciendo? ¡Lo más probable es que seas tú!

En este artículo, analizaremos por qué la capacidad de crear IP base personalizada (celdas y bibliotecas personalizadas) debería ser un factor a la hora de elegir el proveedor de servicios de diseño para su próximo diseño.

El desafío del PPA versus el costo

Los diseños de SoC a menudo superan los límites de potencia, potencia y área (PPA) que se pueden alcanzar con un nodo de proceso asequible. El PPA requerido puede estar justo fuera del alcance. En estos casos normalmente sólo tienes tres opciones:

- Trasladar el diseño a un nodo de proceso más avanzado, complejo y costoso.

- Vuelva a los requisitos de diseño.

- Siga adelante con el diseño a riesgo de no cumplir con los requisitos de diseño.

Nos gustaría considerar una cuarta alternativa: trabajar con un socio de servicios de diseño que pueda desarrollar celdas personalizadas que aprovechen al máximo las capacidades del proceso de fundición. Esto le permite satisfacer sus necesidades de diseño y al mismo tiempo aprovechar un proceso rentable.

Sin embargo, la creación de IP personalizada requiere habilidades especiales en diseño físico. También requiere que los creadores de la propiedad intelectual tengan una relación estrecha con el fabricante. Cambiar la cantidad de carriles de enrutamiento en una biblioteca de celdas, reasignar o cambiar la cantidad de capas metálicas, cambiar el tamaño de los transistores y reorganizar los contactos requiere una comprensión precisa, paso a paso, del proceso objetivo y una buena relación con los ingenieros de procesos.

Un ejemplo de un proyecto de IA

Un ejemplo podría ilustrar el valor de la propiedad intelectual personalizada y cómo su uso encaja en el flujo de diseño.

Faraday Technology trabajó recientemente con un cliente en el desarrollo de un chip para aplicaciones de inteligencia artificial (IA). Como en la mayoría de los escenarios de IA, la potencia informática era el requisito clave del diseño. Sin embargo, el consumo de energía y el costo también fueron cruciales en esta aplicación.

La combinación de requisitos llevó al cliente a elegir un nodo de proceso relativamente maduro en lugar del más avanzado. Los esfuerzos de diseño pronto comenzaron a centrarse en la creación de un plano para la arquitectura innovadora del cliente que lograría los tamaños de chip y el rendimiento previstos.

Este esfuerzo se redujo rápidamente a la configuración de matrices SRAM críticas. Después de experimentar, el cliente concluyó que las opciones IP de SRAM existentes no funcionarían: necesitaban un bloque SRAM personalizado. Entonces comenzaron a conversar con Faraday sobre la creación de un bloque personalizado.

Rediseño de la macro SRAM

Nuestra respuesta comenzó con la recopilación de inteligencia. Un equipo de diseño de IP de Faraday y los arquitectos de chips del cliente discutieron los requisitos para la SRAM personalizada en el contexto de los requisitos generales del chip. También examinamos el proyecto de chip anterior de este cliente y tratamos de comprender su pensamiento arquitectónico y estilo de diseño.

Después del análisis, llegamos a la conclusión de que la SRAM personalizada que el cliente quería era factible en el proceso que eligió. La Figura 1 muestra cómo la nueva macro SRAM personalizada permitió la creación de una nueva huella que redujo el área en un 5 % con la configuración SRAM requerida, una ruta de dirección común y circuitos MBIST.

ilustración 1. Ajuste de IP de SRAM para reducir el área

Aunque las nuevas macros y el plano de planta de SRAM fueron útiles, llegamos a otra conclusión importante: este nodo de proceso no podría soportar el punto PPA del cliente sin ajustes de diseño adicionales.

Personalización de la biblioteca de células predeterminada

Para lograr los objetivos del cliente en este proceso objetivo, tendríamos que optimizar las bibliotecas de células existentes. Esto requeriría cambios en los recursos de enrutamiento de metales (Figura 2).

Figura 2. Recursos estándar para el envío de metales celulares.

Podríamos reorganizar las capas metálicas del proceso para proporcionar suficientes recursos de enrutamiento para lograr el espacio deseado junto con los bloques SRAM personalizados. La Figura 3 muestra cómo agregar dos metales de un solo patrón puede aumentar los recursos de enrutamiento disponibles.

figura 3. Agregar dos capas metálicas de un solo patrón proporcionó más recursos de enrutamiento de celdas estándar

Diseño y simulación de esquinas de proceso.

Finalmente, necesitaríamos diseñar el chip para que funcione en un rango de proceso, voltaje y temperatura (PVT) definido por el usuario al voltaje más alto para el cual podamos garantizar la confiabilidad del chip.

Todos estos cambios fueron ajustes no triviales. Pero juntos colocarían el chip en el punto PPA requerido en el proceso elegido.

llegar a un acuerdo

Una verdad clave sobre la propiedad intelectual personalizada es que el éxito requiere colaboración. Una vez que tuvimos una propuesta para estos ajustes, se la presentamos al cliente junto con nuestra evaluación de su impacto en el diseño. Pasamos por múltiples presentaciones, comentarios y revisiones para llegar a un plan detallado que fue aceptado por nuestro equipo y el cliente.

Una vez que este acuerdo entró en vigencia, pasamos a la Fase 2 de nuestro flujo de diseño de IP básico personalizado, como se muestra en la Figura 4.

Figura 4. Flujo de diseño de IP básico personalizado

Validación de silicio

El siguiente paso fue validar los ajustes en silicio. Esto demostraría que los cambios fueron compatibles con el proceso de fabricación elegido y entregaron los resultados deseados por el cliente.

Primero diseñamos el bloque SRAM personalizado y la nueva biblioteca lógica digital de alta velocidad. Luego creamos estructuras de prueba utilizando la nueva IP, ejecutamos el diseño a través de nuestra cadena de diseño físico, lo pegamos con cinta adhesiva y fabricamos chips de prueba.

La prueba de silicio demostró que los ajustes funcionaron. Esto también nos permitió caracterizar el nuevo IP al nuevo voltaje objetivo. Estos datos permitirían el siguiente paso.

Integración en el flujo de diseño.

Una consideración importante con respecto a la IP personalizada es qué tan fácil (o difícil) será usarla para el equipo de diseño del chip. En este diseño, donde el cliente utilizó el flujo de diseño estándar de Faraday, nuestro objetivo era hacer que la IP personalizada fuera completamente transparente para los diseñadores de chips.

Esto significó integrar los datos de diseño para las personalizaciones en los distintos archivos del Process Design Kit (PDK). De esta manera, las herramientas de planificación, síntesis, sincronización, ubicación y ruta y análisis utilizarían la nueva IP sin ninguna acción especial por parte de los diseñadores de chips.

Cuando el cliente comenzó el diseño, el equipo de IP personalizado de Faraday asumió una función diferente, apoyando al equipo de diseño de chips. Al momento de escribir este artículo, los esfuerzos de diseño de chips aún están avanzando hacia el cierre. No ha habido problemas importantes con la IP personalizada. Todas las técnicas utilizadas en esta personalización se han utilizado antes y la agresiva esquina PVT todavía está dentro del rango de confiabilidad garantizada del chip, por lo que estamos seguros.

La IP personalizada ofrece una alternativa importante

En este diseño, nuestro cliente buscaba un plano de planta y un nivel de rendimiento ligeramente superior a las capacidades de las bibliotecas existentes para el proceso elegido. En lugar de actualizar a un nodo más complejo y costoso, el cliente optó por trabajar con Faraday para crear una IP personalizada que satisfaga sus necesidades de diseño específicas. Le otorgamos la licencia de IP personalizada al mismo precio que la IP estándar fabricada por Faraday, sin cargo adicional por personalización.

La capacidad de utilizar un nodo de proceso más sofisticado con un diseño y costos unitarios más bajos, así como el rendimiento y el impacto en el área de la IP personalizada, deberían combinarse para brindar al cliente una ventaja competitiva en el cada vez más concurrido mercado de chips de IA.

La IP personalizada no puede sustituir la selección de un nodo tecnológico adecuado para un diseño de chip sofisticado. Sin embargo, si la IP estándar de un proceso en particular proporciona un punto de PPA cercano a lo que se necesita y el examen de la arquitectura muestra que existen pocas barreras específicas para lograr los objetivos del diseño, la IP personalizada a menudo puede ser un puente hacia el éxito.

Este breve artículo inevitablemente carece de detalles. Si desea obtener más información sobre este diseño en particular (en la medida en que podamos divulgarlo) o más sobre el programa de propiedad intelectual individual de Faraday, comuníquese con faraday-tech.com.

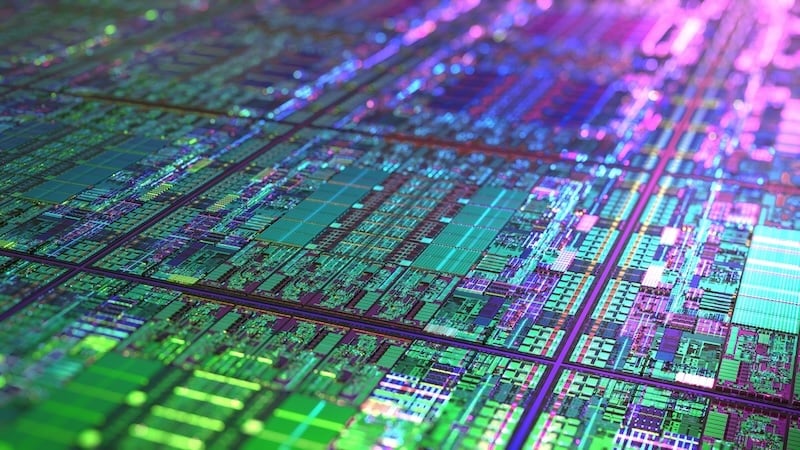

Imagen destacada cortesía de Adobe. Todas las demás imágenes utilizadas son cortesía de Faraday Technology.

Los artículos de la industria son una forma de contenido que permite a los socios de la industria compartir noticias, novedades y tecnología útiles con los lectores de All About Circuits de una manera para la que el contenido editorial no es adecuado. Todos los artículos de la industria se adhieren a estrictas pautas editoriales con la intención de brindar a los lectores noticias, experiencia técnica o historias útiles. Los puntos de vista y opiniones expresados en los artículos de la industria son los del socio y no necesariamente los de All About Circuits o sus autores.

[ad_2]

Deja una respuesta