What you’ll learn:

- Where is a safety-certified network-on-chip needed?

- Why ISO 26262 certification is important for NOC designs.

Software-defined vehicles (SDVs) and advanced driver-assistance systems (ADAS) have placed heavy demands on system-on-chip (SoC) platform designs. Adding in lots of processor, GPU, and artificial-intelligence/machine-learning (AI/ML) cores requires one or more high-performance network-on-chip (NoC) subsystems connecting these components with memory and peripherals. Such setups are utilized in safety-critical application areas like automotive require safety certifications like ISO 262626.

The latest Ncore cache-coherent interconnect toolset from Arteris augments the company’s Ncore non-cache-coherent NoCs. It provides ISO 26262 certification support for ASIL-B through ASIL-D. Ncore works with any processor core like RISC-V and offers pre-validated support for Armv9 cores.

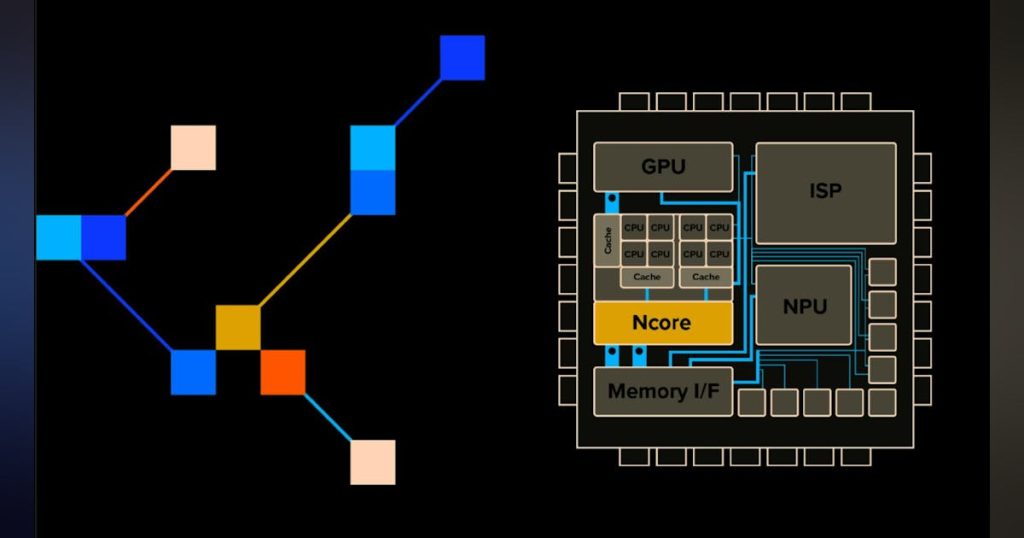

The configurable tool can generate a mix of fully coherent, I/O-coherent, and non-coherent NoC that manages a range of memory and peripheral interfaces (Fig. 1). This includes CHI-E, CHI-B and ACE fully coherent agent interfaces. The ACE-Lite IO coherent interfaces are supported along with AXI for non-coherent subsystems and devices. The NoC can be a mesh or heterogeneous network.

This type of configurable NOC creation can save more than 50 man-years of work compared to designing a NoC from scratch. Arteris is able to optimize for small die areas while supporting low-power requirements and high-performance operation.

Many of these designs are moving toward chiplet implementations, including automotive SoCs (Fig. 2). Likewise, more complex chips often include multiple NoCs of different types, such as coherent and non-coherent networks, based on the requirements of the chiplets connecting different devices.

Having a tool to provide a selection of configurable NoCs saves lots of time and being equipped with an ISO 26262-certified tool also simplifies designs targeting safety applications. The same is true using an interface to pre-validated cores. However, another aspect of the latest output is the integration with Arm emulation support so that a design can be quickly tested.

Deja una respuesta