[ad_1]

En los sistemas integrados, los dispositivos lógicos discretos como la serie 74'HC se utilizan ampliamente en muchas aplicaciones. La ventaja de estos dispositivos lógicos es que funcionan independientemente del microcontrolador (MCU) y pueden responder mucho más rápido que el software. Sin embargo, estos dispositivos se suman a la lista de materiales (BOM) y requieren espacio adicional en la PCB.

Para resolver este problema, muchos microcontroladores Microchip incluyen un periférico llamado Configurable Logic Cell (CLC) en los MCU PIC o un periférico similar llamado Configurable Custom Logic (CCL) en los MCU AVR. Ambos periféricos implementan una lógica personalizada definida por software que puede ejecutarse independientemente de la CPU. En otras palabras, una vez configurada la función lógica personalizada, su comportamiento es independiente del microcontrolador.

Estos periféricos son herramientas útiles para desarrollar circuitos lógicos simples, mezclar señales e integrarse con otros periféricos de hardware. Sin embargo, una limitación de estos periféricos es que la cantidad de lógica por instancia es muy pequeña. Cada CLC es aproximadamente equivalente a una única tabla de búsqueda (LUT), mientras que la CCL es una instancia con algunas LUT independientes.

Presentamos el bloque lógico configurable

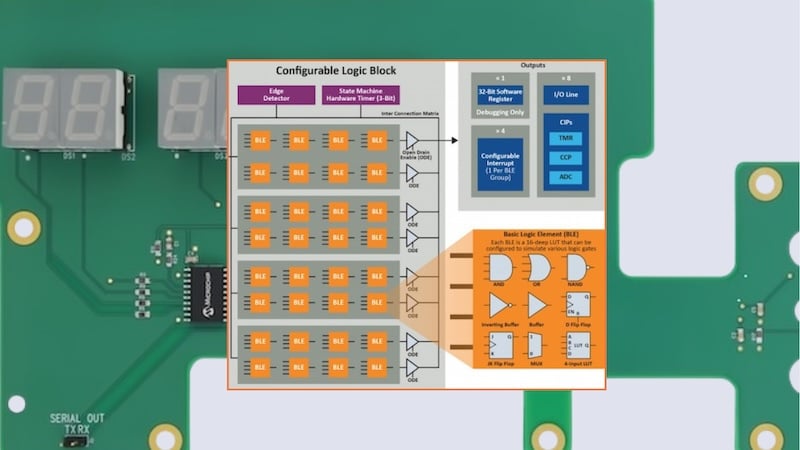

Para admitir aplicaciones más complejas, se desarrolló un nuevo tipo de periférico lógico, el bloque lógico configurable (CLB), como se muestra en la Figura 1. Se introdujo por primera vez en la familia de microcontroladores PIC16F13145.

ilustración 1. Diagrama de bloques del bloque lógico configurable.

Tenga en cuenta que el CLB no necesariamente reemplaza los periféricos CLC o CCL. Los microcontroladores pueden tener tanto CLC/CCL como CLB.

La familia CLB PIC16F13145 consta de cuatro conjuntos de grupos lógicos, cada uno de los cuales contiene ocho elementos lógicos básicos (BLE). Los BLE están conectados a través de grupos lógicos, siendo cada grupo lógico una representación de dos salidas GPIO y una interrupción opcional para la CPU.

Otros elementos del CLB son:

- Un temporizador de hardware dedicado de 3 bits con salidas decodificadas

- Un detector de bordes para señales de entrada.

- Un registro de salida de 32 bits para depuración.

Además, otras salidas periféricas del microcontrolador independientes del núcleo se pueden utilizar como entradas del CLB para diseños más complejos.

El CLB l se inicializa desde la memoria del microcontrolador y puede controlar los pines directamente desde la propia tela a través de Peripheral Pin Select (PPS). PPS permite al usuario reasignar los pines de E/S utilizados con los periféricos de hardware para lograr una mayor flexibilidad de diseño. Por ejemplo, si se usara RA1 para el reloj SPI y RA6 fuera más beneficioso, PPS podría reasignar el pin.

Todos los BLE comparten un reloj común en toda la estructura, cuya fuente se configura en software junto con un divisor de reloj opcional. El CLB puede utilizar una de las fuentes de reloj internas del microcontrolador o una fuente proporcionada externamente. Cuando funcionan a 5,5 V, los BLE tienen un tiempo de propagación típico de menos de 6 ns.

Síntesis CLB

Dado que el CLB es mucho más complejo que el CLC o el CCL, se desarrolló una nueva herramienta llamada sintetizador CLB. El sintetizador CLB proporciona una interfaz gráfica para configurar la lógica, como se muestra en la Figura 2.

Figura 2. El sintetizador CLB demuestra un ejemplo de modulación por cambio de fase (PSK).

Además de las primitivas lógicas, el sintetizador también admite bibliotecas de bloques lógicos de nivel superior que el usuario puede proporcionar previamente o crear a medida.

Al interactuar con la herramienta gráfica, se genera un módulo Verilog detrás de escena para su síntesis. Si el desarrollador prefiere escribir su propio Verilog o tiene un archivo listo, el archivo se puede importar directamente a la herramienta como un módulo.

La salida del sintetizador CLB es un archivo ensamblador que contiene el flujo de bits para configurar el CLB y algo de código fuente para configurar el CLB como periférico. Esta herramienta se puede ejecutar a través del Configurador de código MPLAB (MCC) o mediante una herramienta en línea independiente. El MCC es una utilidad de generación de código que permite a los usuarios instalar y configurar los periféricos del microcontrolador a través de una interfaz visual. Después de configurar los periféricos de hardware, el MCC genera un código de inicialización y una API del dispositivo.

En tiempo de ejecución, el flujo de bits CLB se carga directamente desde la memoria del programa utilizando el hardware integrado. Esta implementación beneficia al programa al permitir cambiar la configuración de CLB mientras el programa se está ejecutando. El proceso de carga se puede repetir con un flujo de bits diferente almacenado en la memoria del dispositivo.

Ejemplos de diseño con el CLB

Para demostrar las aplicaciones de CLB, analizamos dos ejemplos:

- Un convertidor de pantalla de 7 segmentos

- Un conversor de datos serie SPI a WS2812.

Estos ejemplos de aplicaciones son bloques de construcción que se pueden copiar y utilizar como parte de una solución general. Su objetivo es demostrar la utilidad de CLB para los diseños.

Convertidor de pantalla de 7 segmentos

Las pantallas de 7 segmentos se pueden controlar mediante el conjunto normal de pines de E/S. Una implementación estándar normalmente requiere una tabla de búsqueda definida por software para convertir el número de entrada en el patrón de salida correcto para su visualización.

En esta implementación, el CLB actúa como una tabla de búsqueda de hardware. El software carga el carácter de salida deseado (0 a F) en el registro de entrada CLB. Cada segmento de salida de la pantalla está controlado por una LUT que asigna las entradas a las salidas.

Este caso de uso se utilizó internamente para construir un nuevo tablero de control para un sistema de seguimiento del tiempo. La interfaz de usuario original se desarrolló en la década de 1980 utilizando la lógica de la serie 74'HC. Utilizando CLB para mejorar el diseño, un único microcontrolador de 20 pines puede implementar la lógica de la pantalla y el teclado.

Como se muestra en la Figura 3, esto reduce significativamente la lista de materiales (BOM). La placa original anterior tiene muchos más componentes que el nuevo diseño siguiente, que utiliza una MCU con CLB.

figura 3. Comparación del tablero de visualización de 7 segmentos original (arriba) con el nuevo tablero con CLB (abajo). (Click para agrandar)

Convertidor de datos serie SPI a WS2812

WS2812 es un protocolo serie de 1 cable para controlar matrices de LED mediante modulación de ancho de pulso. En este caso, el hardware SPI actúa como un registro de desplazamiento para que los datos se envíen a los LED, mientras que el CLB convierte SCLK y SDO en la salida esperada.

Esto se implementa utilizando un contador monoactivado de 3 bits, un pestillo D con habilitación y una LUT de 4 entradas, como se muestra en la Figura 4.

Figura 4. Diagrama de bloques del convertidor de datos serie SPI a WS2812. (Click para agrandar)

El truco con esta implementación son las fuentes de reloj para SPI y CLB. El reloj SPI está configurado en Idle HIGH, cambia de estado en el flanco ascendente y funciona a la frecuencia de 800 kHz de la salida WS2812. La fuente de reloj de 8 MHz del CLB es 10 veces más rápida.

Cuando SCLK está BAJO, el contador de 3 bits se activa y comienza a contar. Cuando el contador llega a 7 (0b111), se detiene y permanece en 0 hasta el siguiente período bajo del pulso del reloj.

La salida del contador se envía a una LUT de 4 entradas junto con una versión almacenada en caché de los datos de salida. Esto establece el patrón de salida de los datos, que es visible en el lado derecho de la Figura 4. Después de restablecer el contador, la salida del contador permanece en 0 para completar el ciclo. Luego, si es necesario, se transfiere el siguiente byte al hardware SPI y se repite el ciclo.

Ventajas de los bloques lógicos configurables

Ambos ejemplos ilustran la ventaja de la lógica discreta dentro de un microcontrolador. Los periféricos de hardware descargan tareas de la CPU, lo que puede mejorar el tiempo de respuesta y el consumo de energía al tiempo que reduce la cantidad de piezas. El CLB permite el desarrollo de aplicaciones complejas que antes no podían implementarse en un microcontrolador. Actualmente, el CLB se puede encontrar en la familia de microcontroladores PIC16F13145, disponible directamente en Microchip Direct u otros minoristas de electrónica.

Nota del autor: El ejemplo del convertidor de pantalla de 7 segmentos fue desarrollado por Josh Booth, y el ejemplo del convertidor de SPI a WS2812 fue desarrollado por Petre Teodor-Emilian.

Todas las imágenes utilizadas son cortesía de Microchip Technology.

Los artículos de la industria son una forma de contenido que permite a los socios de la industria compartir noticias, noticias y tecnología útiles con los lectores de All About Circuits de una manera para la que el contenido editorial no es adecuado. Todos los artículos de la industria se adhieren a estrictas pautas editoriales con la intención de brindar a los lectores noticias, experiencia técnica o historias útiles. Los puntos de vista y opiniones expresados en los artículos de la industria son los del socio y no necesariamente los de All About Circuits o sus autores.

[ad_2]

New Comments