[ad_1]

DDR5, la DRAM de quinta generación, requiere delicadeza digital-analógica en su MC y DDR PHY. Los tiempos únicos combinados con nuevas tecnologías como 3D XPoint, MRAM y ReRAM marcan un cambio de paradigma

La memoria se utiliza normalmente para almacenar los datos o el código de programa que un procesador de computadora necesita para funcionar. Para realizar esta tarea, se utiliza memoria dinámica de acceso aleatorio (DRAM). DRAM es un tipo común de memoria de acceso aleatorio (RAM) que se utiliza en computadoras personales (PC), estaciones de trabajo y servidores. El acceso aleatorio permite que el procesador de la PC acceda directamente a cualquier porción de la memoria, en lugar de proceder secuencialmente desde un punto de partida.

¿Cómo funciona la DRAM?

La memoria consta de bits de datos o código de programa dispuestos en una cuadrícula bidimensional. La DRAM almacena bits de datos en la llamada memoria o celda de memoria, que consta de un condensador y un transistor. Las celdas de memoria suelen estar dispuestas en una configuración rectangular. Cuando se envía una carga a través de una columna, se activa el transistor de la columna. Una celda de memoria DRAM es dinámica, lo que significa que debe actualizarse o suministrarse con una nueva carga electrónica cada pocos milisegundos para compensar las pérdidas de carga del condensador.

Las celdas de memoria funcionan con otros circuitos que identifican filas y columnas, rastrean el proceso de actualización, le indican a una celda si debe aceptar o no una carga y leen o restauran datos de una celda.

DRAM es una opción de memoria semiconductora que un diseñador de sistemas puede utilizar al construir una computadora. Los tamaños típicos de DRAM oscilan entre 1 y 2 GB para teléfonos inteligentes y tabletas y entre 4 y 16 GB para computadoras portátiles.

Ventajas de la DRAM

- Muy cerca

- Bajo costo por bit

- Estructura de celda de memoria simple

Desventajas de la DRAM

- Proceso de fabricación complejo

- Es necesario actualizar los datos

- Se requieren circuitos externos más complejos (lectura y actualización periódicas).

- Memoria volatil

- Velocidad de funcionamiento relativamente lenta

Procesos de fabricación de DRAM

Los procesos de fabricación de DRAM se denominan 1x-nm, 1y-nm, 1z-nm, 1alpha-nm y 1-beta. Para lograr la capacidad de cada celda de bits, se proporciona una capa dieléctrica específica. Las DRAM 1beta son de bajo consumo y tienen el doble de velocidad de datos 5X (LPDDR5X) y pueden entregar datos a una velocidad de 8,5 Gbit/s. La fabricación de DRAM de nodo 1beta requiere litografía de múltiples patrones combinada con tecnología de proceso de última generación y capacidades de materiales avanzados. La introducción de técnicas eDVFSC (núcleo de extensiones de escalado de frecuencia y voltaje dinámico mejorado) tiene como objetivo mejorar el control de ahorro de energía de las DRAM.

Vienen 1 DRAM de nodo gamma

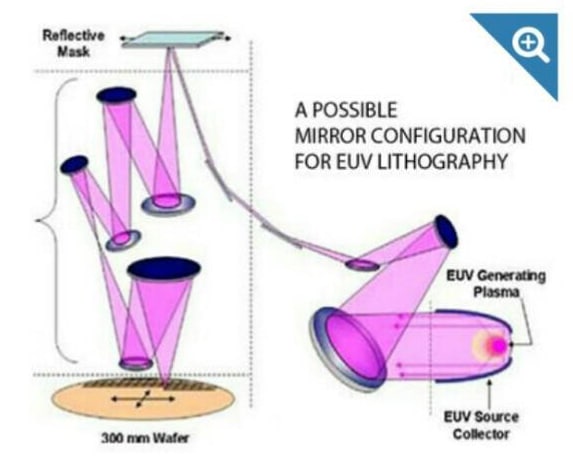

Se espera que esta DRAM avanzada desbloquee un crecimiento exponencial y oportunidades para que florezca una economía digital. Es un paso importante para asegurar la cadena de suministro de semiconductores. Actualmente, Micron es pionera en la fabricación de DRAM. Recientemente, la empresa instaló equipos de producción de litografía ultravioleta extrema (EUV) en sus instalaciones de fabricación de obleas A3 en Taiwán.

En mayo de 2023, Micron anunció que adoptaría esta tecnología de patrones avanzados (EUV) para producir su nodo gamma DRAM-1 de próxima generación. Se espera que esta tecnología proporcione el tamaño de celda más pequeño para DRAM. La desventaja de la litografía EUV es que requiere múltiples patrones, lo que permite que la litografía de 193 nm reduzca significativamente el tamaño de la DRAM. Micron combina nuevos materiales, herramientas y técnicas novedosas para mejorar su alineación de múltiples patrones.

| Tabla 1 SRAM frente a DRAM | ||

| parámetro | SRAM | DRACMA |

| Velocidad de lectura/escritura | Mas rapido | Más lento que SRAM |

| el consumo de energía | Más | Menos |

| Estructura interna | Complejo | Más fácil que SRAM |

| densidad | Menos denso | Muy cerca |

| Utilizada en | Memoria caché | Memoria principal |

| Memoria por bit | Puede almacenar más bits por chip | No se pueden almacenar muchos bits por chip |

| Componente de almacenamiento | transistor | condensador |

| Precio | Caro | Más económico que SRAM |

Desafíos para la industria DRAM

El código de corrección de errores de un solo chip (ECC) es una característica especial en la industria DRAM que corrige errores de bits en chips DRAM, aumentando la confiabilidad y las tasas de error. ECC requiere memoria adicional en la que se almacenan los códigos ECC en el momento de escribir la memoria en la DRAM. Los códigos Hamming se utilizan en dichos sistemas ECC para proporcionar detección de errores de un solo bit y de dos bits por ráfaga. Las DRAM más recientes, como LPDDR5 y DDR5, admiten ECC de un solo chip.

Martillo de hilera

Las mismas filas o las adyacentes se activan repetidamente, lo que resulta en una pérdida o cambio del contenido de datos en las filas sin dirección. Las últimas versiones de DRAM LPDDR5/DDR5 admiten la gestión de actualizaciones (incluidos DRFM y ARFM) para abordar este desafío.

Temperatura del dispositivo

Los usuarios deben consultar con el proveedor de DRAM sobre el rango de temperatura en el que funcionará la DRAM. Por encima de cierta temperatura, se pierde la integridad de los datos.

Pérdida de rendimiento

La DRAM puede perder su contenido debido a un corte de energía. Por lo tanto, se requiere memoria de respaldo no volátil, donde se debe copiar el contenido de la DRAM antes de desconectar la energía. Cuando se restablece la energía, el contenido almacenado en la memoria no volátil se vuelve a escribir en la DRAM.

Las especificaciones de DDR5 y Lpddr5 establecidas por el Joint Electron Device Engineering Council (JEDEC), un organismo de estándares de la industria que rige las especificaciones de DRAM, se muestran en la Tabla 2.

| Tabla 2 Especificaciones de DDR5 y Lpddr5 | ||

| factor | DDR5 | Lpddr5 |

| Densidad máxima de viruta | 64 Gbit | 32 Gbit |

| Velocidad de datos máx. | 6,4 Gbps | 6,4 Gbps |

| Tamaño máximo UDIMM (DSDR) | 128GB | N / A |

| canales | 2 | 1 |

| Ancho de banda | 64 bits (2×32) | 16 bits |

| Bancos de memoria | 4 | dieciséis |

| Grupos bancarios | 08/04/23 | 4 |

| Longitud de ráfaga | LB 16×2 | V16 |

| Recoger por adelantado | 16n | 16n |

| Voltaje (Vdd) | 1,1 V | 1,05 V |

| vddq | 1V | 0,5 V |

DDR5 MC y PHY

DDR5 se describe como una DRAM síncrona de doble velocidad de datos de quinta generación diseñada para el procesamiento de datos de próxima generación. El controlador de memoria (MC) DDR5 y DDR PHY son dos componentes principales para un rendimiento eficiente de la DRAM. DDR5 MC requiere expertos en diseño digital, mientras que DDR5 PHY requiere experiencia tanto digital como analógica. Para cada aplicación, DDR5 tiene una gran cantidad de parámetros de temporización y registros de configuración. Cada proveedor debe tener sus propios parámetros de sincronización y valores de registro de configuración únicos. La interfaz DDR5 PHY (DFI) es un protocolo de interfaz que define tiempos, señales y parámetros programables necesarios para transferir datos hacia y desde DRAM al MC. En muchas situaciones, MC y PHY se desarrollan por separado y, a menudo, por diferentes empresas.

DRAM de próxima generación

Las DRAM actuales aumentan la latencia y el consumo de energía, lo que se conoce como “muro de la memoria”. Las DRAM de próxima generación han desarrollado nuevas funciones para abordar estos desafíos. Introducido por Intel en 2015, 3D XPoint se describe como la próxima generación de DRAM. 3D XPoint se basa en una tecnología llamada Memoria de cambio de fase (PCM) y se utiliza en SSD y DIMM. PCM almacena información en las fases amorfa y cristalina.

La industria ahora también está desarrollando otros nuevos tipos de memoria, como la RAM magnetorresistiva (MRAM) y la RAM resistiva (ReRAM). Al igual que 3D XPoint, MRAM y ReRAM se pueden fabricar y vender como dispositivos independientes.

3D XPoint no se vende como almacenamiento integrado. Por el contrario, MRAM y ReRAM también se pueden utilizar en los mercados de memoria integrada. Para MRAM, la industria está desarrollando una tecnología de próxima generación llamada MRAM de par de transferencia de giro (STT-MRAM). STT-MRAM utiliza el magnetismo del espín de los electrones para proporcionar propiedades no volátiles en chips, combinando la velocidad de SRAM y la no volatilidad del flash con una vida útil ilimitada.

En la memoria tradicional, los datos se almacenan como una carga eléctrica. Por el contrario, MRAM utiliza una celda de memoria de unión de túnel magnético (MTJ) como elemento de almacenamiento. La RAM ferroeléctrica (FRAM) es otra tecnología a la que hay que prestar atención. FRAM utiliza un condensador ferroeléctrico para almacenar datos y es una memoria no volátil con gran capacidad de almacenamiento. Nantero, una empresa privada, tiene más de 170 patentes de nanotubos para reemplazar las DRAM. Es posible tener cientos y miles de estos nanotubos en cada celda de memoria para formar una red de elementos resistivos para formar una memoria de acceso aleatorio no volátil (NVRAM). Sin duda, las DRAM de próxima generación ofrecen numerosas oportunidades para los OEM.

Nuestras necesidades de almacenamiento pasadas, presentes y futuras en el mundo electrónico son mucho mayores de lo que esperamos. En el mundo web, la información se puede mantener viva a través de la memoria. DRAM ofrece una visión diferente de la memoria electrónica y una comprensión diferente del «mecanismo de almacenamiento de datos».

El autor, Vinayak Ramachandra Adkoli, Es licenciado en producción industrial y trabajó durante diez años como profesor en tres escuelas técnicas diferentes. También es escritor y dibujante independiente.

[ad_2]

New Comments