[ad_1]

En Embedded World 2024, SiTime presentó Chorus, su última familia de generadores de reloj centrados en centros de datos. El Chorus Clock System-on-Chip (ClkSoC) basado en MEMS es el primer generador de reloj integrado diseñado para instalaciones de centros de datos de inteligencia artificial.

El chip utiliza un resonador MEMS de silicio en lugar de un cristal de cuarzo en su corazón. Quartz, que durante mucho tiempo ha sido el estándar de la industria para la sincronización precisa, a menudo alcanza sus límites en las condiciones operativas que se encuentran en los grandes centros de datos, como los que se utilizan para las pilas de modelos de lenguaje grande (LLM) de IA generativa. El resonador MEM que alimenta a Chorus es más adecuado para su uso en un entorno de centro de datos caluroso y eléctricamente ruidoso.

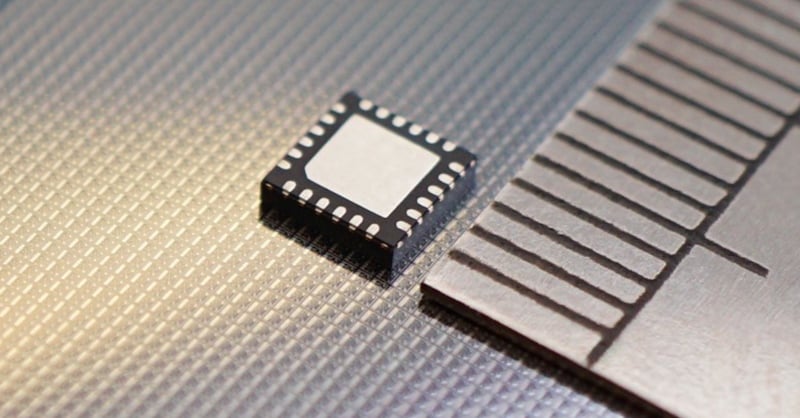

Paquetes QFN de 24 pines SiT91213 y SiT91211 de 4×4 mm.

Chorus integra el resonador MEMS, el circuito del oscilador y un IC de reloj en un solo chip. Esto elimina la necesidad de cristales externos y simplifica significativamente la arquitectura del reloj del sistema. Esto reduce el tiempo de desarrollo, el número de piezas y el espacio en la placa, al tiempo que mejora la capacidad de fabricación, la confiabilidad y el rendimiento del sistema.

Características principales del Coro

Los chips generadores de reloj Chorus están disponibles en un QFN de 24 pines, 4 mm x 4 mm y 0,5 mm de paso con bordes humectables. El tamaño pequeño permite una mayor flexibilidad en el diseño de PCB, y el QFN de paso pequeño con flancos humectables garantiza una capacidad de fabricación constante, una refrigeración eficiente de los componentes y un funcionamiento fiable a largo plazo.

En comparación con los dispositivos basados en cristal de cuarzo, SiT91213 o SiT91211 ofrecen una capacidad de carga diez veces mayor cuando funcionan con el resonador MEMS. Las piezas cuentan con muy baja fluctuación, salidas de frecuencia programables y estabilidad de alta frecuencia (±20 ppm y ±50 ppm de -40°C a 105°C).

Un solo SiT91213 o SiT91211 puede reemplazar múltiples osciladores independientes (izquierda), ya que puede controlar cuatro cargas diferenciales u ocho cargas de un solo extremo (derecha).

Los dos chips son idénticos excepto por las especificaciones de fluctuación:

- SiT91211: fluctuación baja a 150 femtosegundos (fs)

- SiT91213: Jitter ultrabajo a 70 fs

Las piezas cuentan con un rango de frecuencia ajustable de 1 MHz a 700 MHz, un dominio de reloj configurable y cuatro salidas diferenciales u ocho de un solo extremo. Las salidas de reloj se pueden controlar como LVDS, HCSL, LVPECL o LVCMOS.

SiTime crece para satisfacer las necesidades de sincronización de los centros de datos

Aunque cualquier dispositivo de alta velocidad requiere una sincronización de alta calidad, los centros de datos operan en condiciones de ruido térmico y eléctrico que superan con creces los requisitos de la mayoría de los sistemas independientes. Los centros de datos mueven y procesan cantidades masivas de datos a través de muchos dominios físicos y de reloj. Los datos deben sincronizarse a través de interconexiones en chip de alta velocidad, buses de chip a chip y buses entre dispositivos. La fluctuación, el giro y la deriva son aún más importantes en un entorno tan crítico.

SiTime tiene una larga trayectoria en la producción de dispositivos de cronometraje de precisión con especial énfasis en el rendimiento en comparación con la tecnología tradicional. Mientras que los circuitos de temporizador tradicionales utilizan un cristal de cuarzo discreto o un oscilador de cristal híbrido como estándar de frecuencia principal de alta precisión, los chips de temporizador de coro eliminan el cuarzo y la fuente externa.

Diagrama de bloques interno de SiT91213 y SiT91211.

SiTime ha desarrollado una fuente de frecuencia MEMS de silicio que supera el rendimiento de los cristales de cuarzo y se puede integrar fácilmente en un SoC con otros componentes clave. Los chips SiTime combinan el resonador MEMS con el circuito oscilador, PLL, distribución de reloj y circuito controlador. También agrega GPIO e I2C/SPI para comunicación y control.

Según SiTime, el resultado de esta integración avanzada es una fuente de reloj unificada de múltiples salidas que puede reducir el espacio de PCB en un 50% debido a la reducción del número de piezas y la capacidad de reemplazar cuatro circuitos osciladores separados con un chip.

Herramientas de desarrollo y disponibilidad.

SiTime ofrece la placa de evaluación SiT6520EB para acelerar el diseño y el aprendizaje del sistema. Los chips se están enviando a clientes estratégicos ahora (abril de 2024) y se espera que se envíen para disponibilidad general en la segunda mitad de 2024.

Todas las imágenes utilizadas son cortesía de SiTime.

[ad_2]

New Comments