[ad_1]

La solución de software de matriz múltiple de Tessent puede ayudar a simplificar las tareas críticas de diseño para prueba (DFT) para circuitos integrados (IC) complejos basados en arquitecturas 2.5D y 3D.

La búsqueda de desarrollar dispositivos compactos y energéticamente eficientes ha empujado a los diseñadores a crear circuitos integrados más eficientes y densos en energía. Estos dispositivos de próxima generación están habilitados mediante el uso de arquitecturas 2.5-D y 3-D que conectan chips verticalmente (IC 3-D) o uno al lado del otro (2.5-D) para que se conecten como un comportamiento de dispositivo individual. Para simplificar el proceso, Siemens Digital Industries Software ha lanzado una nueva solución de software llamada Tessent Multi-Die Software Solution.

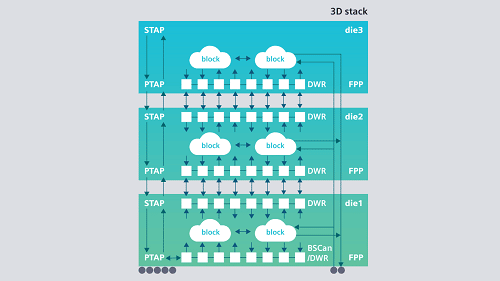

La rápida adopción e implementación de diseños de chips densos en dispositivos 2.5D y 3D ha aumentado la complejidad de las pruebas de circuitos integrados. Para solucionar este problema, la solución de software de matriz múltiple de Tessent puede generar patrones de conexión de matriz a matriz y permitir pruebas a nivel de paquete utilizando el lenguaje de descripción de exploración de límites (BS DL). El nuevo software puede funcionar sin problemas con otras herramientas de software a través de una plataforma Tessent integrada, lo que reduce el tiempo de prueba hasta 4 veces.

Según la compañía, el software Tessent Multi-Die es una de las soluciones de automatización DFT más completas para tareas DFT altamente complejas relacionadas con diseños de circuitos integrados 2.5D y 3D. El software se puede utilizar con otro software de la serie Tessent, como el software Tessent TestKompress Streaming Scan Network y el software Tessent IJTAG, que optimizan los recursos de prueba DFT para cada bloque sin preocuparse por el impacto en el resto del diseño, agilizando DFT planificación e implementación para la era 2.5D y 3D IC. Este software permite a los diseñadores crear rápidamente hardware compatible con IEEE 1838 con arquitecturas IC 2.5D y 3D.

“A medida que las limitaciones de los enfoques de diseño de circuitos integrados 2D tradicionales se vuelven más evidentes con el tiempo, más equipos de diseño están adoptando las ventajas de potencia, rendimiento y factor de forma que pueden ofrecer las arquitecturas de circuitos integrados 2.5D y 3D. Pero la implementación de estos esquemas avanzados en nuevos diseños comienza sin establecer primero una estrategia DFT que reconozca los desafíos inherentes que plantean estas arquitecturas, que pueden aumentar los costos y socavar los cronogramas agresivos”, dijo Laurie Balch, presidenta y directora de investigación de Pedestal Research. «Sin embargo, al hacer evolucionar la tecnología DFT para seguir el ritmo de la rápida adopción de diseños multidimensionales, los proveedores de EDA pueden desempeñar un papel clave para permitir aún más la adopción generalizada global de arquitecturas 2.5D y 3D».

principales características

• Acelera y simplifica significativamente las tareas críticas de planificación e implementación de DFT para los circuitos integrados de próxima generación basados en arquitecturas 2.5D y 3D

• Permite la generación rápida de hardware compatible con IEEE 1838 para arquitecturas IC 3D

• Extrae un solo lenguaje de descripción de exploración de límites (BSDL) a nivel de paquete y genera patrones

• Extrae BSDL de troquel a troquel y genera patrones entre troqueles basados en exploración de límites

• Admite el puerto paralelo flexible (FPP) IEEE 1838 al aprovechar las capacidades de entrega de datos en paquetes de Tessent Streaming Scan Network (SSN) que optimizan los recursos de prueba DFT para cada bloque sin preocuparse por el impacto en el resto del diseño

• Capacidad para cumplir y admitir varios estándares diferentes, como IEEE 1687 e IEEE 1149.1

• Integración perfecta con otros productos Tessent a través de una plataforma Tessent integrada

[ad_2]