[ad_1]

Investigadores de Penn State han demostrado un método novedoso de integración 3D utilizando materiales 2D. Este avance, detallado en su estudio reciente, aborda el creciente desafío de empaquetar más transistores en áreas cada vez más pequeñas, una preocupación clave en la industria de los semiconductores a medida que los dispositivos se vuelven más pequeños y requieren una funcionalidad mejorada.

El número de transistores en un chip se duplicará cada dos años, según la Ley de Moore, un concepto de escala clave para dispositivos electrónicos que garantiza una mayor potencia informática, pero hay un límite.

Los procesadores más potentes de la actualidad tienen alrededor de 50 mil millones de transistores en un área del tamaño de una miniatura. Según los expertos de Penn State, cada vez es más difícil colocar más transistores en esta pequeña área.

Saptarshi Das, profesor asociado de ingeniería y mecánica y coautor del estudio, y sus colegas proponen una solución en un estudio publicado el 10 de enero.Th2023 en la revista especializada. Naturaleza: Integración fluida de la integración 3D con materiales 2D.

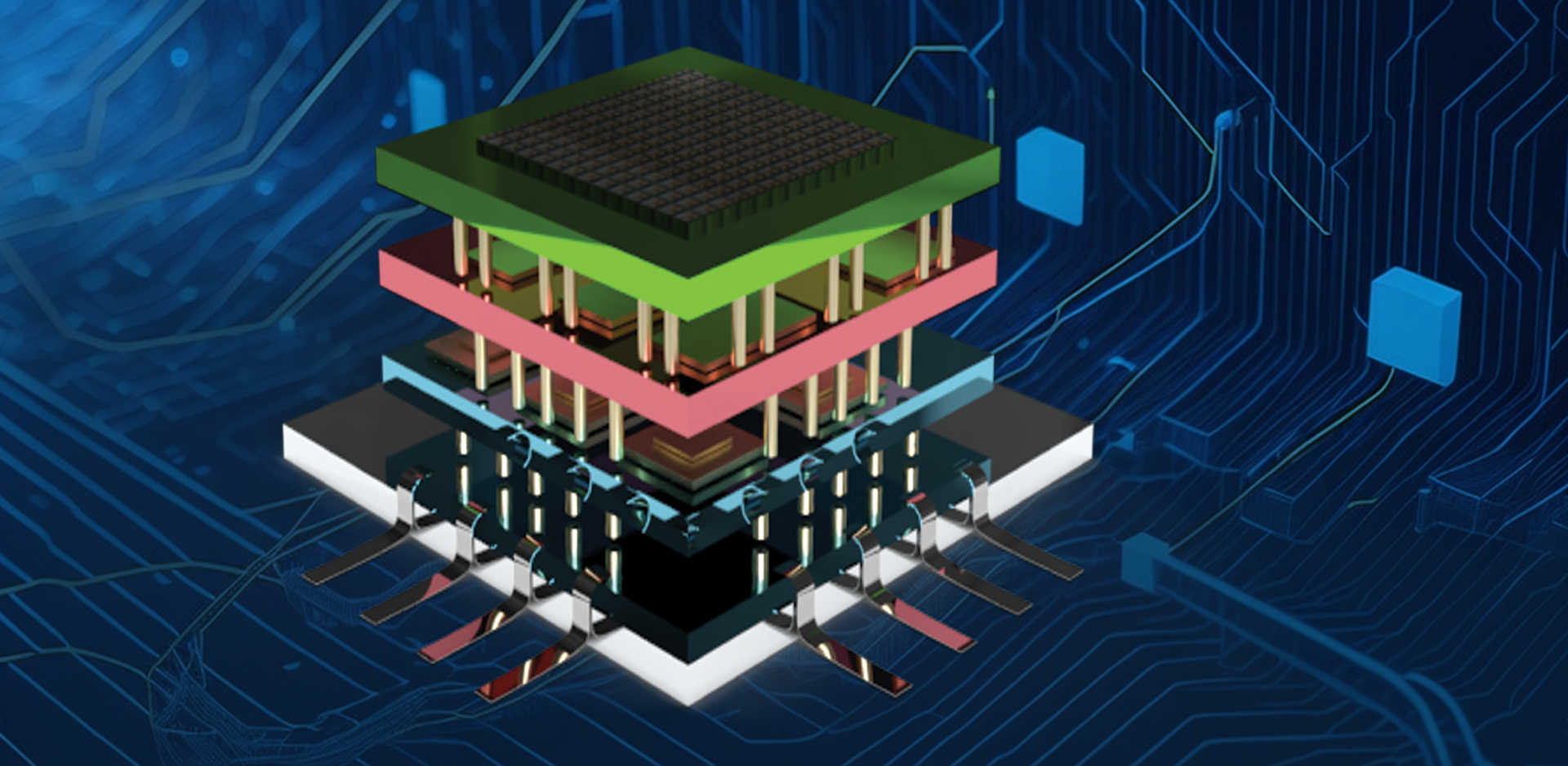

En la industria de los semiconductores, la integración 3D se refiere al apilamiento vertical de múltiples capas de componentes semiconductores. Este método no sólo hace que sea más fácil colocar más transistores basados en silicio en un chip de computadora -un proceso conocido como «More Moore»- sino que también permite el uso de transistores hechos de materiales bidimensionales para integrar diferentes funcionalidades en diferentes capas del Stapels: un concepto conocido como «Más que Moore».

A través del trabajo descrito en el estudio, Saptarshi y el equipo muestran que además de escalar la tecnología existente, existen formas prácticas de lograr «Más Moore y Más que Moore» a través de la integración monolítica 3D. En lugar de apilar capas fabricadas por separado como en el pasado, los investigadores están construyendo los dispositivos directamente uno encima del otro mediante una integración monolítica 3D.

La integración 3D monolítica ofrece la mayor densidad de conexiones verticales porque no depende de unir dos chips prediseñados, lo que requeriría microgolpes al conectar dos chips, lo que le brinda más espacio para realizar conexiones.

Najam Sakib, coautor del estudio e investigador asociado, Universidad Estatal de Pensilvania

Sin embargo, Darsith Jayachandran, investigador asociado en ingeniería y mecánica y coautor del estudio, señala que la integración monolítica 3D plantea problemas importantes porque los componentes tradicionales de silicio se derretirían a las temperaturas de procesamiento.

Un desafío es el límite superior de temperatura del proceso de 450 grados Celsius (C) para la integración back-end de chips basados en silicio: nuestro enfoque de integración 3D monolítica reduce significativamente estas temperaturas por debajo de 200 °C. Los presupuestos de temperatura de proceso incompatibles hacen que la integración 3D monolítica sea un desafío para los chips de silicio, pero los materiales 2D pueden soportar las temperaturas requeridas por el proceso.

Darsith Jayachandran, cocorresponsal del estudio e investigador asociado, Universidad Estatal de Pensilvania

Aunque los investigadores utilizaron métodos existentes, fueron los primeros en lograr una integración 3D monolítica a esta escala mediante el uso de dicalcogenuros de metales de transición, un tipo de semiconductor 2D, para fabricar transistores 2D.

Se trata de añadir funciones nuevas y útiles a nuestros dispositivos electrónicos, como mejores sensores, una mejor gestión de la batería u otras funciones especiales para hacer que nuestros dispositivos sean más inteligentes y versátiles.

Muhtasim Ul Karim Sadaf, investigador asociado, Universidad Estatal de Pensilvania

La computación con mayor eficiencia energética también fue posible gracias a la capacidad de la integración 3D para apilar dispositivos verticalmente, resolviendo un problema inesperado con componentes tan pequeños como los transistores en un chip de computadora: el espaciado.

Al apilar dispositivos verticalmente, se reduce la distancia entre dispositivos, lo que reduce el retraso y también el consumo de energía.

Rahul Pendurthi, cocorresponsal del estudio e investigador asociado, Universidad Estatal de Pensilvania

Los investigadores lograron lograr “Más Moore” reduciendo la distancia entre dispositivos. Además, los investigadores cumplieron el requisito «Más que Moore» utilizando transistores fabricados con materiales bidimensionales.

Las propiedades ópticas y eléctricas especiales de los materiales 2D, como su sensibilidad a la luz, los hacen ideales para su uso como sensores. Los investigadores afirmaron que esto es útil dado el creciente número de dispositivos periféricos y dispositivos conectados, como sensores meteorológicos domésticos inalámbricos y teléfonos celulares que recopilan datos en el «borde» de una red.

Muhtasim Ul Karim Sadaf, investigador en ingeniería y mecánica y coautor del estudio, explicó: ““Más que Moore” se refiere a un concepto en el mundo de la tecnología en el que fabricamos chips de computadora no sólo más pequeños y más rápidos, sino también con más funcionalidad. Se trata de añadir funciones nuevas y útiles a nuestros dispositivos electrónicos, como mejores sensores, una mejor gestión de la batería u otras funciones especiales para hacer que nuestros dispositivos sean más inteligentes y versátiles.«

Los investigadores descubrieron que el uso de dispositivos 2D para la integración 3D ofrece otros beneficios. La movilidad superior de los portadores es una de las propiedades de los materiales semiconductores que describe la forma en que se transfiere una carga eléctrica. Otra razón es su extrema delgadez, que permite a los investigadores agregar más potencia informática y más transistores a cada capa de integración 3D.

El estudio demostró la integración 3D a gran escala y caracterizó decenas de miles de dispositivos, a diferencia de la investigación académica típica que utiliza pequeños prototipos. Das afirma que este logro cierra la brecha de conocimiento entre académicos y empresas y podría allanar el camino para más colaboraciones en las que las empresas aprovechen los recursos y la experiencia de Penn State en materiales 2D.

La disponibilidad de dicalcogenuros de metales de transición a escala de oblea de alta calidad producidos por científicos del Consorcio de Cristales Bidimensionales (2DCC-MIP) de la Universidad Penn State, una instalación nacional para usuarios, y la Plataforma de Innovación de Materiales de la Fundación Nacional de Ciencias de EE. UU. (NSF) hizo que el escalamiento posible Avance posible.

Charles Ying, director del programa de Plataformas de Innovación de Materiales de NSF, añadió: «Este avance demuestra una vez más el papel esencial de la investigación de materiales como base de la industria de semiconductores y de la competitividad de Estados Unidos. Años de esfuerzos del Consorcio de Cristales Bidimensionales de la Universidad Penn State para mejorar la calidad y el tamaño de los materiales 2D han hecho posible lograr la integración 3D de semiconductores a una escala que puede ser transformadora para la electrónica.«

Se afirma que esto es sólo el comienzo del progreso tecnológico.

Él notó, «Nuestra capacidad para demostrar una gran cantidad de dispositivos a escala de oblea demuestra que hemos podido traducir esta investigación a una escala valorada por la industria de los semiconductores. Construimos 30.000 transistores en cada capa, lo que puede ser una cifra récord. Esto coloca a Penn State en una posición única para liderar parte del trabajo y colaborar con la industria de semiconductores de EE. UU. para avanzar en esta investigación.«

Además de Das, Jayachandran, Pendurthi, Sadaf y Sakib, otros autores incluyen a Andrew Pannone, estudiante de doctorado en ingeniería y mecánica; Chen Chen, profesor asistente de investigación en 2DCC-MIP; Ying Han, investigador postdoctoral en ingeniería mecánica; Nicholas Trainor, candidato a doctorado en ciencia e ingeniería de materiales; Shalini Kumari, investigadora postdoctoral; Thomas McKnight, estudiante de doctorado en ciencia e ingeniería de materiales; Joan Redwing, directora de 2DCC-MIP y profesora distinguida de ciencia e ingeniería de materiales e ingeniería eléctrica; y Yang Yang, profesor asistente de ingeniería y mecánica.

El estudio fue apoyado por la Fundación Nacional de Ciencias y la Oficina de Investigación del Ejército.

Referencia de la revista:

Jayachandran, D., et. Alabama. (2023) Integración tridimensional de transistores de efecto de campo bidimensionales. Naturaleza. doi:10.1038/s41586-023-06860-5.

Fuente: https://www.psu.edu/

[ad_2]