[ad_1]

Las redes neuronales profundas han dado lugar a avances significativos en la IA generativa, pero su arquitectura plantea un desafío para lograr una eficiencia óptima. Descubra cómo IBM Research se inspira en el cerebro humano para mejorar los sistemas cognitivos digitales.

Las redes neuronales profundas son responsables de muchos avances en la inteligencia artificial generativa (IA). Su diseño incluye una estructura que actúa como un obstáculo virtual, impidiendo alcanzar una eficiencia óptima. La arquitectura, que consta de diferentes módulos para memoria y procesamiento, ejerce una presión significativa sobre los recursos del sistema al facilitar la comunicación entre estos componentes. Esto conduce a velocidades de procesamiento más lentas y a una eficiencia general reducida.

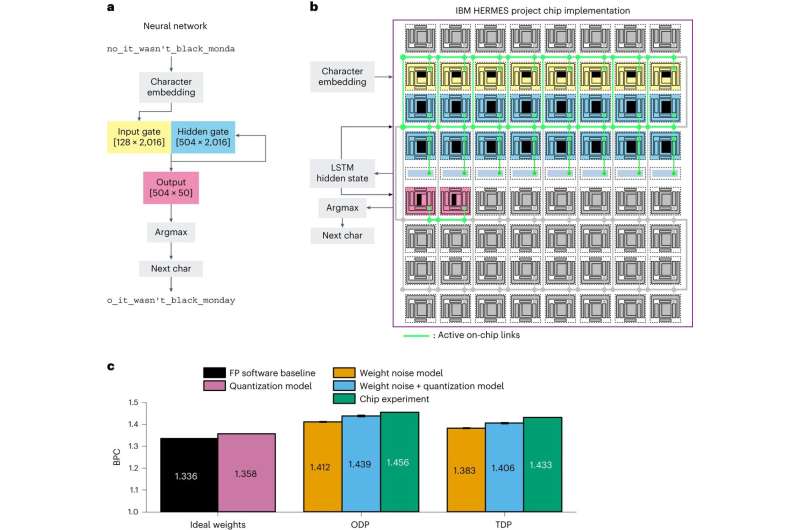

Inspirándose en el modelo más eficiente, el cerebro humano, IBM Research ha desarrollado una solución para aumentar la eficiencia de los sistemas cognitivos digitales. Presentaron un chip informático en memoria de señal mixta de 64 núcleos basado en una memoria de cambio de fase para la inferencia profunda de redes neuronales. Este enfoque implica el desarrollo de un chip de IA de señal mixta que tiene el potencial de aumentar la eficiencia y al mismo tiempo minimizar el consumo de batería en los esfuerzos de IA.

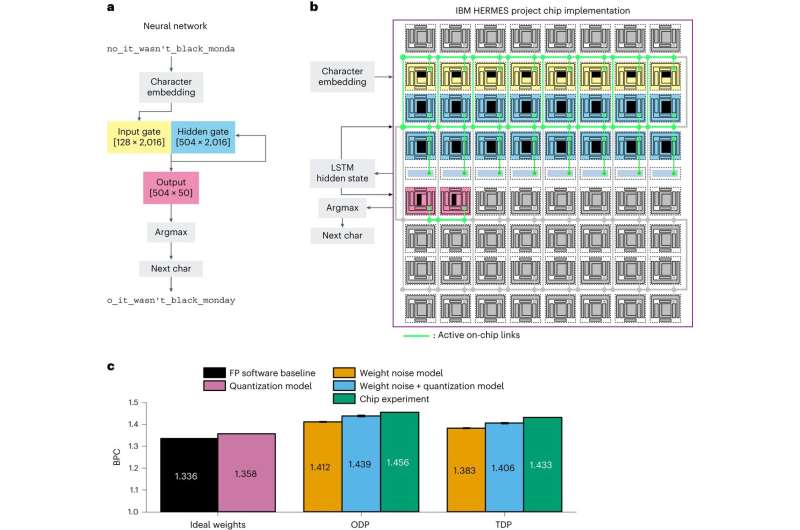

«El cerebro humano muestra rendimiento consumiendo poca energía», señaló Thanos Vasilopoulos, coautor del estudio del laboratorio de investigación de IBM en Zurich, Suiza. Un chip de señal mixta refleja la interacción de las sinapsis en el cerebro y consta de 64 núcleos analógicos en memoria, cada uno de los cuales alberga varias unidades de células sinápticas. Los convertidores se utilizan para garantizar un cambio perfecto entre los estados analógico y digital. Los chips alcanzaron una precisión del 92,81%.

El grupo de investigación demostró una precisión de inferencia acercándose a equivalentes basados en software utilizando ResNet (red neuronal residual) y redes de memoria a corto plazo. ResNet es un modelo de aprendizaje profundo que permite el entrenamiento en numerosas capas de redes neuronales sin sacrificar el rendimiento. La integración de la computación analógica en memoria (AIMC) y las operaciones y comunicaciones digitales en el chip es esencial para lograr mejoras integrales tanto en latencia como en eficiencia energética. Sus hallazgos incluyen un chip AIMC de múltiples núcleos fabricado utilizando tecnología complementaria de semiconductores de óxido metálico de 14 nm, con memoria de cambio de fase de back-end integrada.

El mayor rendimiento abre la puerta a ejecutar cargas de trabajo grandes y complejas en entornos caracterizados por recursos limitados de energía o batería. Esta capacidad integral se extiende a aplicaciones en teléfonos móviles, automóviles y cámaras. Los proveedores de servicios en la nube se beneficiarán del uso de estos chips para reducir sus costos de energía y minimizar su impacto en el medio ambiente.

A través de este esfuerzo, se han validado en silicio numerosos componentes críticos para aprovechar todo el potencial de la IA analógica y garantizar una IA de alto rendimiento y eficiencia energética. Un chip informático en memoria de señal mixta totalmente integrado sin precedentes basado en una memoria de cambio de fase (PCM) integrada de back-end en un proceso CMOS (semiconductor de óxido metálico complementario) de 14 nm.

Estas celdas constan de 64 núcleos AIMC, cada uno equipado con una matriz de memoria con 256×256 celdas unitarias. Estas células se ensamblan cuidadosamente utilizando cuatro dispositivos PCM, por un total de más de 16 millones de dispositivos. Junto con la matriz de memoria analógica, cada núcleo integra una unidad de procesamiento digital liviana que realiza funciones de habilitación, acumulación y operaciones de escalado”.

[ad_2]